La Cina verso l’autarchia tecnologica

È dagli anni '90 che, da dietro gli scranni e le scrivanie delle stanze del…

Kepler, Maxwell, Denver, Tegra: dove va NVidia?

In una luminosa mattina californiana del novembre 2010, Jensen Huang, fondatore, presidente e CEO di…

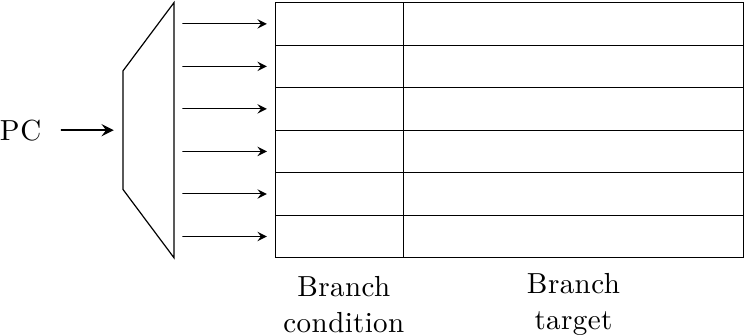

Branch prediction (parte seconda): Predittori semplici

Nello scorso articolo abbiamo visto perchè la Branch Prediction è una componente essenziale dei processori…

European MS DOS 4

Sul web è facile farsi un’idea di quelli che, temporalmente, sono i principali sistemi operativi…

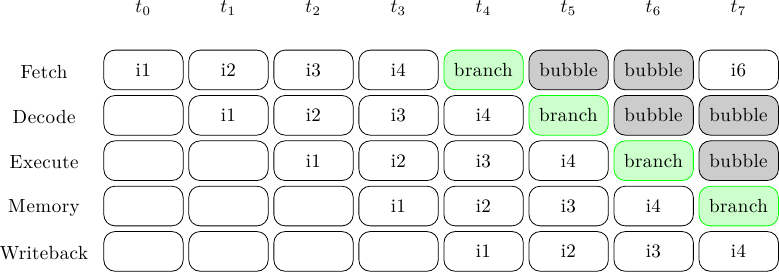

Processori superscalari out-of-order: Branch prediction (parte prima)

Dopo una lunghissima pausa (causa tapeout) eccoci di nuovo qui con una nuova puntata sull'architettura…

Faggin premiato da Obama

Abbiamo approfonditamente parlato di Federico Faggin e della nascita del primo microprocessore della storia in…

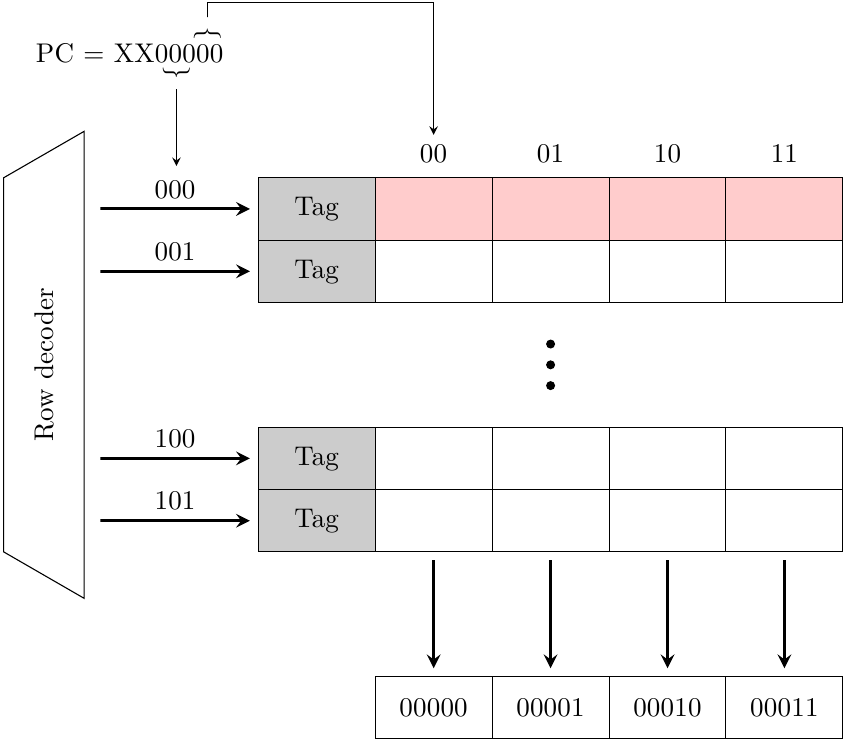

Processori superscalari out-of-order: lo stadio di fetch

In-order o out-of-order, superscalare o meno, il viaggio delle istruzioni all'interno di qualsiasi CPU comincia…

Un pezzo d’Italia nei Microprocessori

Siamo abituati ad attribuire le grandi innovazioni del settore informatico ad aziende e a tecnici…

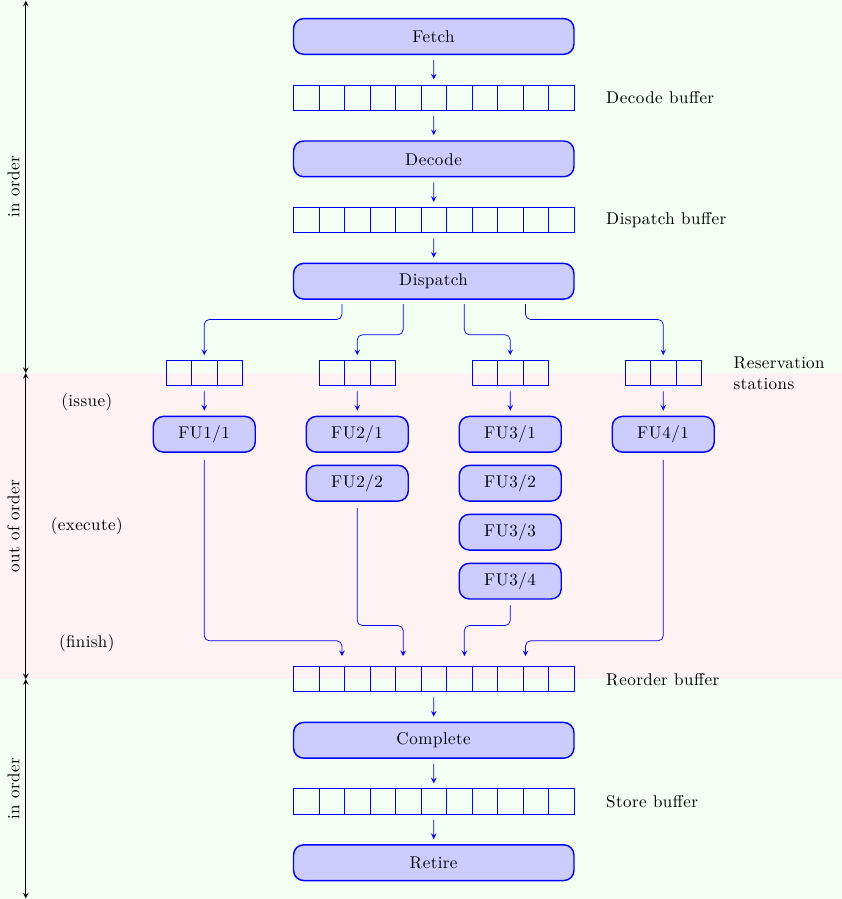

Processori superscalari out-of-order: una vista d’insieme

Finalmente, dopo una lunga peregrinazione tra pipeline semplici e diversificate, oggi comincia una nuova serie…

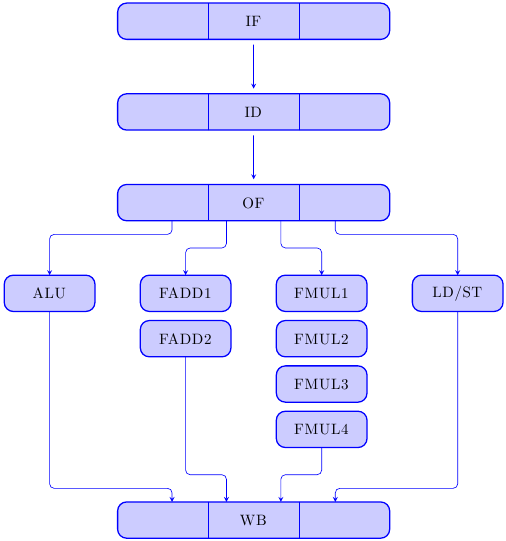

Oltre la pipeline semplice: le pipeline diversificate

Nello scorso articolo abbiamo visto come pipeline profonde diventino rapidamente inefficienti a causa dell'aumento del…