Photonic CPUs still have a lot to clarify (and be expected)

A scientific publication has recently appeared concerning what is being hailed as a revolution in…

Le CPU fotoniche hanno ancora parecchio da chiarire (e da farsi aspettare)

Di recente è apparsa una pubblicazione scientifica riguardo ciò che viene decantata come una rivoluzione…

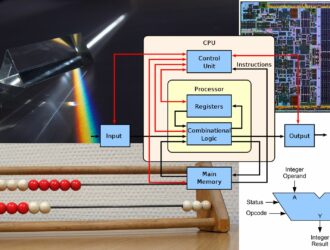

NEx64T – 9: conclusions

The series dedicated to the new NEx64T architecture has come to an end, after being…

NEx64T – 9: conclusioni

La serie dedicata alla nuova architettura NEx64T è arrivata al capolinea, dopo averla confrontata con…

NEx64T – 8: comparison with other architectures

The previous article completed the overview of NEx64T, so it is now possible to have…

NEx64T – 8: confronto con altre architetture

Il precedente articolo ha completato la panoramica di NEx64T, per cui è adesso possibile disporre…

NEx64T – 7: the new SIMD/vector unit

With the hot potato of the x86/x64 legacy out of the way, let us now…

NEx64T – 7: la nuova unità SIMD/vettoriale

Tolta di mezzo la patata bollente dell'eredità di x86/x64, passiamo adesso a esaminare la nuova…

NEx64T – 6: the legacy of x86/x64

Legacy is an inescapable concept when it comes to x86 and x64 architectures, so after…

NEx64T – 6: il legacy di x86/x64

Il legacy è un concetto imprescindibile quando si parla delle architetture x86 e x64, per…