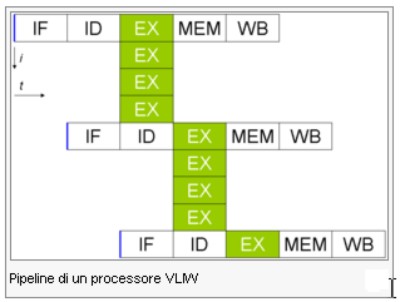

Superscalare e vliw nel mondo GPU

La scorsa settimana avevamo introdotto alcuni tra i più comuni approcci al calcolo parallelo e…

Calcolo parallelo: modelli a confronto

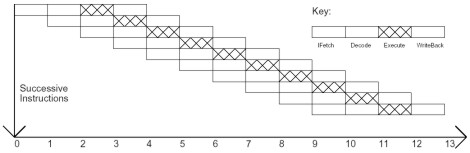

La scorsa settimana abbiamo introdotto alcuni concetti tra cui, in particolare, quello di pipeline. Si…

Pipeline: la catena di montaggio informatica

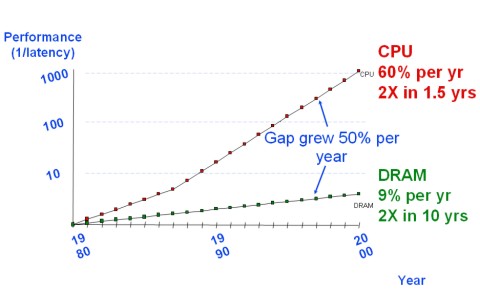

Dopo aver passato brevemente in rassegna le tipologie di memorie presenti al'interno di un chip,…

Grafica: una questione di memoria.

Dopo aver analizzato la genesi delle primitive di un'immagine 3D e aver iniziato ad introdurre…

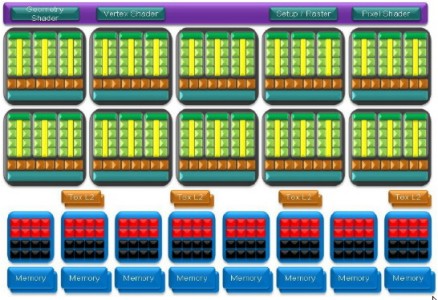

ATi e nVidia: due differenti approcci allo stesso problema

Nell'articolo della scorsa settimana si è iniziato ad affrontare il discorso relativo all'architettura a blocchi…

Il 3D, dalla teoria alla pratica: schema a blocchi di una GPU

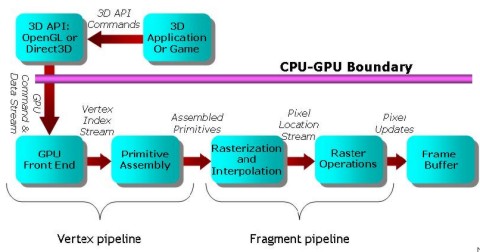

Dopo aver passato in rassegna le varie fasi della "costruzione" delle geometrie di una scena…

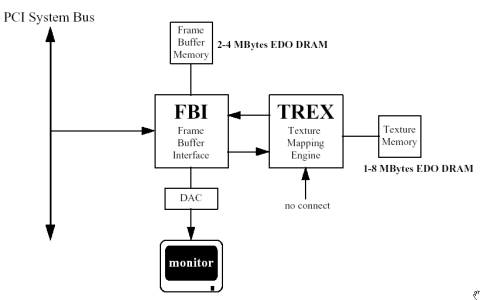

3Dfx: pensieri e parole (con qualche immagine)

Il nome di 3dfx, per chi è appassionato di 3D e videogame su pc, evoca,…

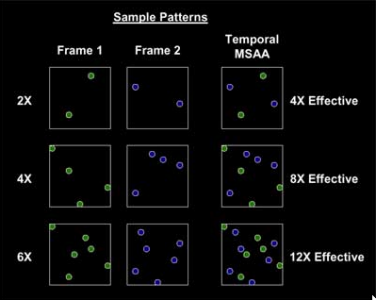

Tecniche di filtraggio: Antialiasing III parte.

Nello scorso articolo avevamo iniziato a descrivere le tecniche di antialiasing utilizzate dai produttori di…

Tecniche di filtraggio: Antialiasing II parte.

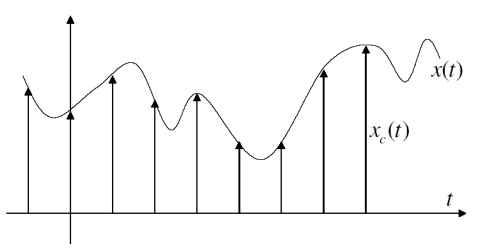

Nella scorsa puntata erano state sommariamente descritte le principali forme di aliasing ed erano state…

Tecniche di filtraggio: Antialiasing I parte.

Nell'ultima puntata di questa rubrica, si era arrivati al termine delle operazioni di tipo geometrico…