APX: la nuova architettura di Intel – 4 – Vantaggi & pecche

Finito di passare in rassegna tutte le novità di APX (con l'ultimo articolo che analizzava…

APX: la nuova architettura di Intel – 3 – Nuove istruzioni

Dopo aver discusso delle funzionalità innovative di APX, passiamo alle nuove istruzioni che sono state…

APX: la nuova architettura di Intel – 2 – Innovazioni

Dopo il primo articolo introduttivo su APX, che ha esposto anche il formato del nuovo…

APX: la nuova architettura di Intel – 1 – Introduzione

A poca distanza della proposta di X86-S, Intel presenta la più grande novità in assoluto…

AmigaOne X1000 si prepara per il Natale…

La macchina più chiacchierata del mondo Amiga "NG" (New Generation) è senza dubbio l'AmigaOne X1000,…

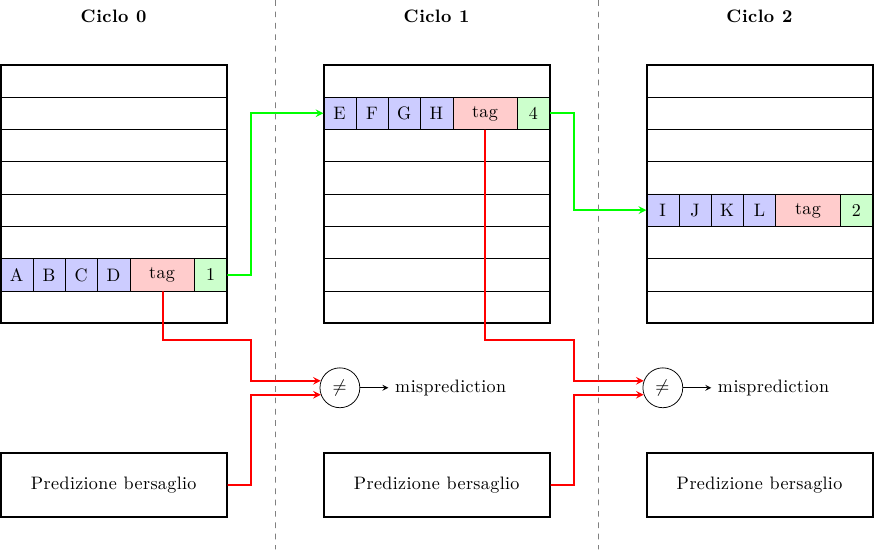

Branch prediction (parte settima): High-frequency fetch

Per trent'anni, prima che il raggiungimento del power wall terminasse la "corsa ai GHz" e…

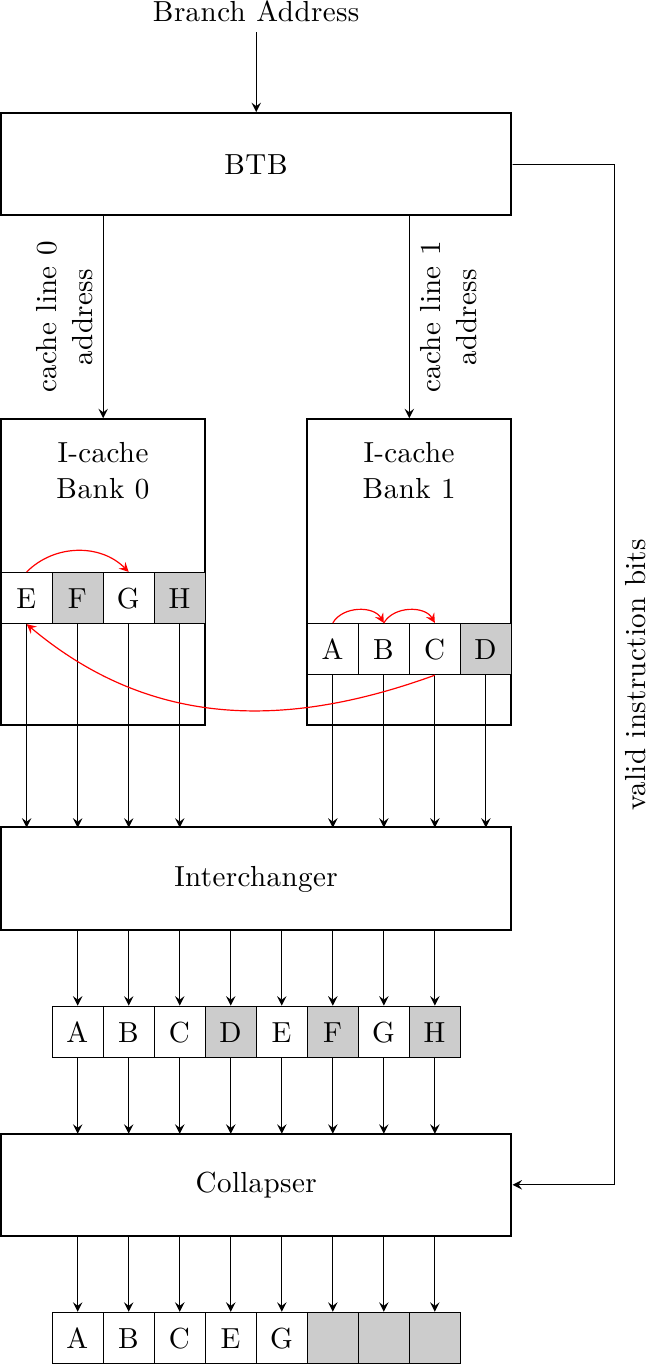

Branch prediction (parte sesta): High-bandwidth fetch

In tutta la discussione sui meccanismi di branch prediction (e siamo ormai alla sesta puntata!)…

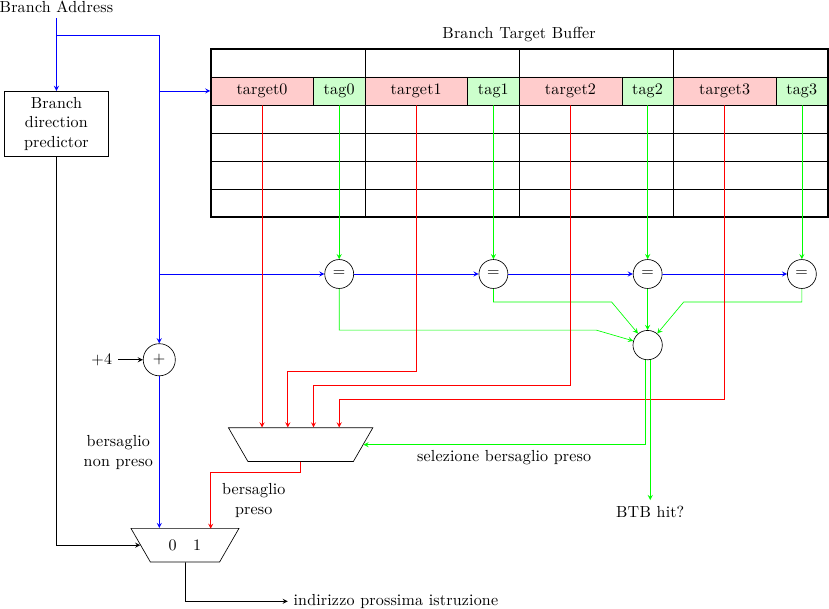

Branch prediction (parte quinta): Predizione del bersaglio

Negli scorsi articoli abbiamo visto alcune tecniche utilizzate dai processori moderni per predire la direzione…

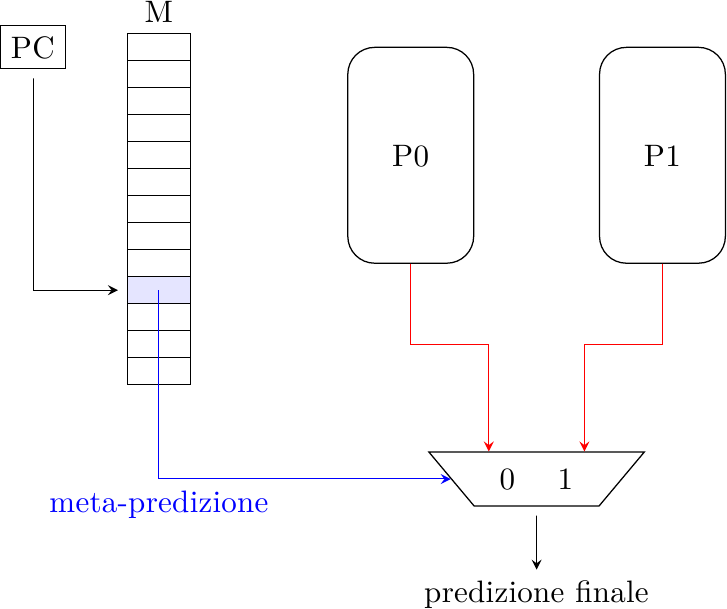

Branch prediction (parte quarta): Predittori ibridi

Nei precedenti due articoli (qui e qui) ho brevemente descritto alcuni schemi di branch prediction,…

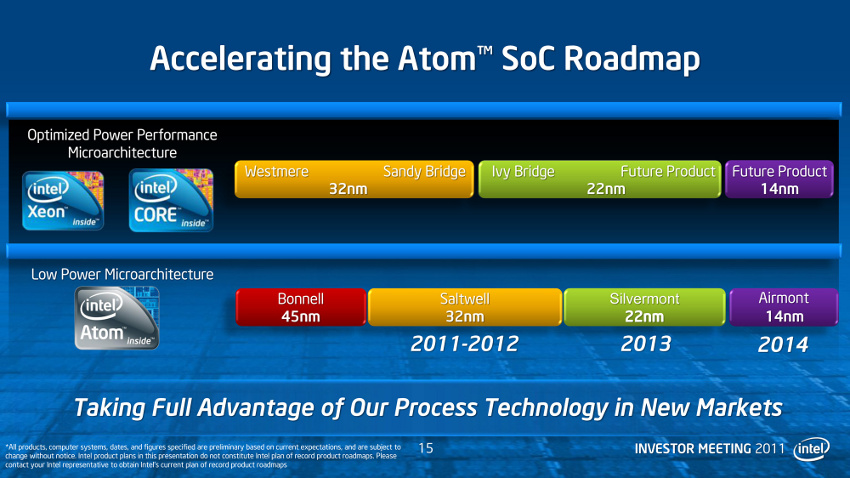

Intel come GlobalFoundries: una strada tutta da scoprire

Qualche giorno fa è comparsa su Reuters una strana e intrigante notizia a proposito di…