Statistiche su x86 & x64 – parte 5 (indirizzamento verso la memoria)

Dopo aver discusso della distribuzione e frequenza del numero di operandi, questa volta puntiamo l'attenzione…

Statistiche su x86 & x64 – parte 4 (numero di operandi)

Le istruzioni, come sappiamo, sono composte dallo mnemonico, che identifica il tipo di azione svolta,…

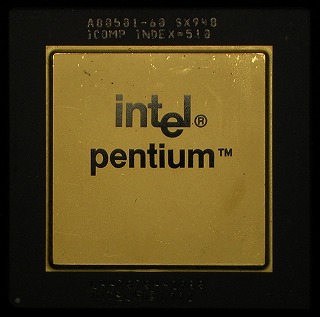

20anni dal lancio commerciale del Pentium

Il primo Intel Pentium è stato ufficialmente commercializzato il 22 marzo del 1993, cambiando in…

Statistiche su x86 & x64 – parte 3 (ISA / istruzioni a confronto)

Dopo l'analisi e i freddi numeri riportati nei precedenti articoli, passiamo a verificare il codice…

Statistiche su x86 & x64 – parte 2 (distribuzione per dimensione)

Proseguiamo con l'analisi del codice delle ISA x86 e x64 dal punto di vista statistico,…

Statistiche su x86 & x64 – parte 1 (macrofamiglie di istruzioni)

La lunga serie sull'analisi dell'aspetto "legacy" di x86 e x64 si era conclusa con l'annuncio…

Le console non sono più il punto di riferimento tecnologico

Ieri sera Sony ha svelato le proprie carte presentando la quarta generazione della sua console…

Freescale (ex Motorola) “ufficializza” la fine dei PowerPC

I PowerPC sono una della famiglie di microprocessori più conosciute e apprezzate, ma il cui…

Il legacy di x86 & x64 – parte 9 (conclusioni)

Dopo aver sezionato l'architettura x86 a caccia di elementi che possano essere classificati come legacy,…

Il legacy di x86 & x64 – parte 8 (SIMD: MMX, 3DNow!, e… SSE)

Ci sono voluti 7 articoli per trattare di una problematica che nasce col capostipite della…