Negli ultimi giorni, si è assistito alla pubblicazione di una serie di notizie riguardanti l’operazione comunemente nota come die shrink e i problemi ed i vantaggi ad essa connessi. Ad iniziare dalla notizia del passaggio a 55 nm della serie GT200 di nVidia, alla notizia degli studi condotti sui cosiddetti chip “probabilistici” o imprecisi, che si prefiggono lo scopo di ridurre notevolmente le tensioni di alimentazione dei processori contenendo drasticamente i consumi, a scapito di una “ragionevole” minor precisione.

Negli ultimi giorni, si è assistito alla pubblicazione di una serie di notizie riguardanti l’operazione comunemente nota come die shrink e i problemi ed i vantaggi ad essa connessi. Ad iniziare dalla notizia del passaggio a 55 nm della serie GT200 di nVidia, alla notizia degli studi condotti sui cosiddetti chip “probabilistici” o imprecisi, che si prefiggono lo scopo di ridurre notevolmente le tensioni di alimentazione dei processori contenendo drasticamente i consumi, a scapito di una “ragionevole” minor precisione.

A queste si aggiunge lo shrink a 45 nm del Cell, la cpu progettata da IBM che ha trovato notorietà presso il grande pubblico per il fatto che, tra le altre cose, equipaggia la Playstation 3.

Ma quali vantaggi dà la riduzione delle geometrie di un chip? D’istinto verrebbe da rispondere: maggiori rese produttive; consumi più contenuti, maggiori frequenze di funzionamento. Quindi, in poche parole, maggior risparmio e prestazioni superiori.

In linea di massima la precedenti affermazioni sono tutte vere ma il passaggio da un processo produttivo ad un altro non è sempre lineare, esente da problemi e di facile ed immediata realizzazione.

Innanzitutto si deve distinguere tra due tipologie di shrink, definite full node ed half node rispettivamente. Si distinguono tra di loro poiché, mentre la seconda comporta una semplice riduzione delle geometrie del chip, la prima obbliga a ridisegnare buona parte delle librerie e a riprogettare le interfacce tra il silicio e le metallizzazioni e, in molti casi, le disposizioni degli stessi connettori metallici.

Per quale motivo ciò avviene?

Intorno al 1965, Gordon Moore iniziò a formulare una serie di ipotesi, frutto di osservazioni relative al ritmo di crescita della complessità dei processori ed all’aumento dei costi dei macchinari che servivano a produrre quei processori. Queste osservazioni, raggruppate e rese organiche, divennero vere e proprie leggi che, nonostante la modifica dei ritmi di crescita nel corso degli anni, conservano ancora una loro validità.

Il raddoppio delle prestazioni previsto da Moore era fissato, originariamente, ogni 12 mesi. Negli ultimi anni si è assistito ad un rallentamento di questa crescita, passando a 18 e, in qualche caso, anche a 24 mesi. I motivi di questi rallentamenti sono molteplici ma, tra i principali, ci sono sicuramente i problemi che sono iniziati a sorgere nel momento in cui ci si è accorti che diventava sempre più difficile operare una riduzione dei consumi e un contenimento delle temperature e dei fenomeni parassiti indesiderati, al diminuire delle geometrie.

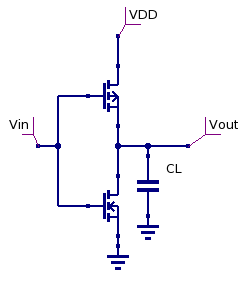

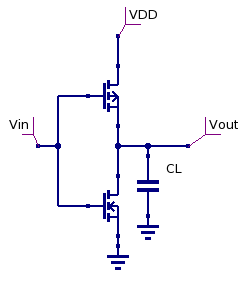

Il passaggio da tecnologie “ibride” nmos, bipolari, cmos alla tecnologia cmos “pura”, permise di ridurre drasticamente il problema della dissipazione termica e di raggiungere livelli di integrazione impensabili in precedenza. Un circuito cmos, in teoria, non dissipa potenza statica.

Nella pratica, tutta una serie di effetti “indesiderati” (correnti di sottosoglia, carica e scarica di capacità parassite, dispersioni delle giunzioni, correnti di cortocircuito durante la commutazione tra le fasi di pull up e pull down delle due reti p-mos e n-mos di cui un circuito cmos è costituito, ecc), del tutto irrilevanti in un circuito relativamente semplice, rappresentano, ormai, circa la metà della potenza che viene dissipata in un circuito VLSI.

La presenza di questi fenomeni rende sempre più complicata la progettazione e lo scaling di circuiti complessi come quelli di una moderna cpu o gpu e costringe all’adozione di tecnologie sempre più sofisticate e costose per tenerli sotto controllo.

La conseguenza pratica è che, nel momento in cui si fa un’operazione di scaling, ci si può ritrovare a veder aumentati gli effetti parassiti con una diminuzione del rapporto segnale rumore. Per riequilibrare il giusto valore (e possibilmente incrementarlo), si adottano soluzioni che tendono a ridurre, ad esempio, fenomeni come il transistor latchup che è un “accoppiamento” capacitivo parassita tra transistor contigui tramite l’utilizzo di “trincee” ricavate tra i transistor che hanno lo scopo di isolarli fisicamente; oppure mediante tecniche come la SOI di IBM (usata anche per il cell) che consiste nel depositare il silicio su strati di materiali isolanti.

Un’altra tecnica è quella nota come low-k; consiste nell’uso di materiali a basso accoppiamento “capacitivo” da interporre tra le connessioni metalliche per ridurre, anche in questo caso, l’effetto “condensatore”, con due piste adiacenti che fanno da armature.

Una tecnica usata per il duplice scopo di migliorare il SNR e ridurre le tensioni di alimentazione del circuito è quella che prevede l’uso di materiali high-k. In questo caso si utilizza un materiale ad elevato accoppiamento capacitivo da interporre nel canale source-drain del transistor, in modo che l’accoppiamento tra gate e source, che pilota i transitori, richieda una tensione di ingresso inferiore in valore assoluto.

Questo permette di ridurre, di conseguenza, anche la tensione di alimentazione (Vdd) e contenere le correnti di leakage. Al diminuire della lunghezza del canale source-drain, diminuisce, di conseguenza, anche la resistenza e, conseguentemente, si deve ridimensionare, in proporzione, anche la larghezza dello stesso canale, per evitare che le correnti di leakage aumentino in maniera incontrollabile.

Un’altra strategia atta a ridurre le correnti di dispersione è quella conosciuta come strained silicon: in parole povere, si “stira” il silicio per creare una direzione privilegiata per il movimento delle cariche, riducendo la loro dispersione in altre direzioni.

Tutte queste tecnologie possono essere adoperate anche contemporaneamente su uno stesso wafer. Ovviamente ognuna di esse fa aumentare il costo del silicio.

Tornando alle due tipologie di shrink. Dovrebbe risultare chiaro, a questo punto, che a volte la riduzione delle geometrie non comporta una crescita preoccupante dei suddetti fenomeni ed, in tal caso, si può procedere alla semplice operazione di miniaturizzazione.

Processi di tipo half node, in ambito gpu, sono stati, ad esempio, il passaggio da 90 a 80 nm e quello da 65 a 55 nm. Al contrario, shrink full node sono quelli in cui si rende necessario intervenire con l’adozione di tecniche per il contenimento dei fenomeni parassiti.

A questa classificazione sommaria, se ne aggiunge un’altra: poiché non tutti i chip che vengono prodotti adottando un determinato node saranno adibiti allo stesso scopo (i 65 nm non servono, ad esempio, solo per cpu o gpu, ma anche per chip meno complessi e non destinati ad equipaggiare sistemi ad elevate prestazioni), possono esistere differenti tipologie dello stesso processo produttivo, che potremmo definire LP (low power process), per circuiti non destinati a lavorare ad alte frequenze o a dissipare elevate potenze e G (general purpose process), per circuiti di dispositivi di tipo high end.

Questa distinzione può portare alla necessità di modificare le librerie di un processo produttivo meno raffinato, qualora questo sia di tipo LP e il suo shrink richiede caratteristiche di tipo G. In tal caso, uno shrink che dovrebbe rientrare nella categoria degli half node rischia di trasformarsi in un full node.

A fronte di tutte queste considerazioni, sembra che un’operazione di shrink sia quasi controproducente. Di fatto, non è così, in quanto, a bilanciare le molte difficoltà ci sono degli innegabili vantaggi. Il principale è che la riduzione delle dimensioni del chip permette di ricavare molti più die dallo stesso wafer.

Ad esempio, nel caso proprio del Cell, passando da 65 a 45 nm si ottiene un ridimensionamento del die da 174 a 115 mm^2 che, tenendo conto degli scarti sui bordi, può portare ad un incremento di oltre 150 unità per singolo wafer (rispetto alle 350-360 attuali). Questo aumento è in grado di compensare abbondantemente gli aumenti di costo del wafer, imputabili all’utilizzo di un processo più “raffinato” e anche eventuali costi di R&D per aggiornare le librerie esistenti, qualora si fosse reso necessario.

Quindi, maggiori economie, consumi più bassi e, qualora servisse, persino prestazioni più elevate.

Unico inconveniente è che ci stiamo avvicinando al limite di questa tecnologia. Il rallentamento nella corsa al raddoppio delle prestazioni è un indice delle sempre maggiori difficoltà che si stanno incontrando nella ricerca delle soluzioni che consentano di mantenere un buon livello del SNR senza arrivare a costi esorbitanti per la ricerca di nuovi materiali e tecnologie.

In futuro avremo modo di tornare su questi argomenti ed approfondirne o spiegarne alcuni aspetti. Lo scopo di questa breve esposizione era soltanto quello di introdurre alcuni argomenti su cui si avrà modo di tornare in futuro.

Quindi, spero che non me ne vogliano né coloro che sono perfettamente a conoscenza degli argomenti toccati e che possono giudicare la trattazione poco stimolante e neppure coloro che non conoscono niente di questi argomenti e che hanno sentito parlare di cose aliene per nulla illustrate in modo da facilitarne la comprensione.

Capisco anche che sarebbe stato molto più interessante parlare di alu, tmu, controller, antialiasing, ecc. e che non è necessario parlare del silicio e della sua lavorazione per affrontare questi argomenti.

Però un’introduzione, magari frammentaria e poco approfondita, può aiutare a chiarire le motivazioni di scelte come quelle, ad esempio, di decidere di seguire la strada delle architetture multicore, oppure del perché far uso di un compilatore per l’gestire l’ILP di un chip o, magari, di ciò che c’è dietro la decisione di sacrificare un’intera produzione di chip per passare alla successiva generazione nel più breve tempo possibile.